RISC-V MCU与加解密IP核之间通过NICE接口连接,通过指令集预留的custom指令控制,custom的指令编码格式如下图所示,RSA使用custom3指令,详细的指令的设计如下表所示。

RSA custom3指令列表

Func7 | Func3 | 指令定义 | 指令含义 | |

Custom3 | 0000000 | 010 | Load_key | 载入密钥 |

0000001 | 010 | Load_data | 载入明文 | |

0000010 | 010 | Load_A | 载入参数A | |

0000011 | 010 | Laod_C | 载入参数C | |

0000100 | 010 | Load_N | 载入模数 | |

0000101 | 010 | Write_back | 写回加解密结果 | |

0000110 | 000 | Start_work | 开始加密 |

NICE指令的编码格式

二、控制状态机

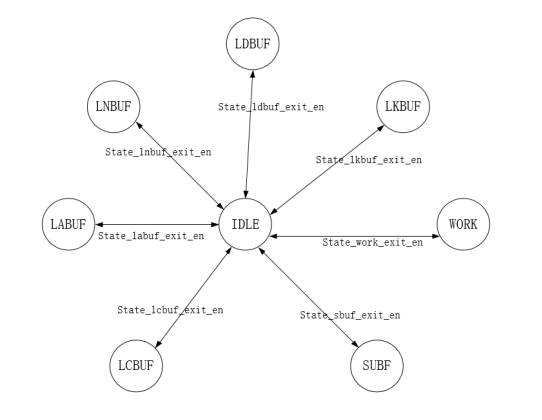

NICE接口状态机控制逻辑,配合RSA加解算法核,完成从RISC-V核存储器中获取明文、密钥、模数、参数A和参数C数据的任务,并根据custom指令,控制RSA加解密算法核完成加解密,并把加解密完成后的数据返回到RISC-V核中。NICE接口中的状态机跳变如下图所示,状态跳变表如下表所示。

状态跳变表

Custom指令 | 状态 | 描述 |

IDLE | 译码状态 | |

Load_key | LKBUF | 从mcu内存装载密钥 |

Load_data | LDBUF | 从mcu内存装载明密文 |

Write_back | SBUF | 返回加解密结果到mcu |

Load_A | LABUF | 从mcu内存装载参数A |

Load_C | LCBUF | 从mcu内存装载参数C |

Load_N | LNBUF | 从mcu内存装载参数N |

Start_work | WORK | 开始加解密 |

状态跳变图

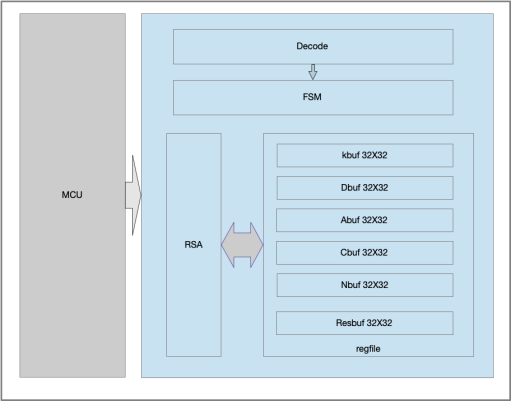

在NICE_CORE接口模块中,为了满足RSA的加解密需求,设置了6个32X32位的寄存器,分别存储明文,密钥,参数A、参数C、模数N及加解密结果,NICE接口控制逻辑的系统架构下图所示。

NICE接口控制逻辑的系统架构

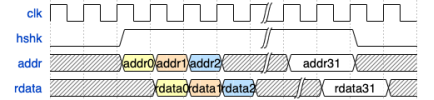

通过NICE接口预留的4个通道,NICE请求,NICE反馈,存储器请求和存储器反馈通道传输数据与控制信号,通过存储器反馈通道从MCU获取数据的时序如下图所示。

NICE接口从MCU获取数据时序图

通过拉高memory_hold_up,占用LSU通道,连续传输32个32位的数据,存储到对应的寄存器堆中。待全部数据加载完毕,NICE核会根据对应的控制指令将数据加载到加解密核中,进行加解密。加解密完成后complete信号拉高,将完成的数据存储到resregfile中,NICE核收到write_back指令,会将regfile中的数据通过存储器反馈通道写回MCU中,完成整个加解密流程。