俄罗斯为电脑打造RISC-V处理器:8核、2 GHz、12纳米

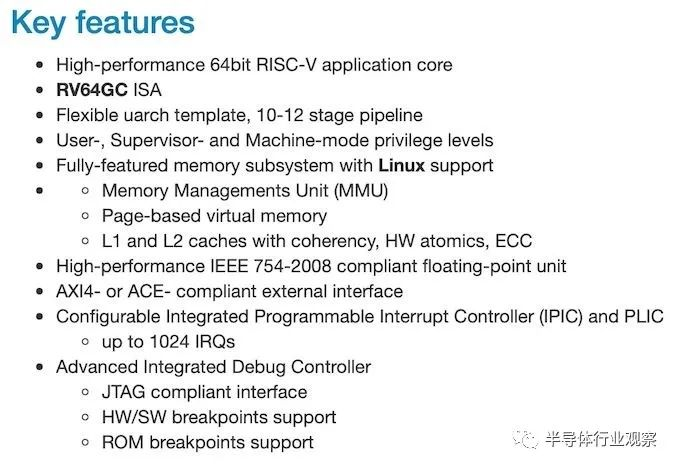

据俄罗斯媒体Vedomosti.ru今天报道称,俄罗斯国有企业集团 Rostec 已与服务器公司 Yadro 和芯片设计公司 Syntacore 达成协议,三方将合作为计算机、笔记本电脑乃至服务器开发 RISC-V 处理器。初步报告表明,到 2025 年,Syntacore 将开发足够强大的 RISC-V 设计,为政府和教育系统提供动力。据报道,该项目的成本约为 300 亿卢布(4 亿美元),该项目的组织者计划销售 60,000 个基于包含 RISC-V 内核作为主要处理内核的新处理器的系统。报道称,他们目标是使用 12 纳米工艺构建一个运行频率为 2 GHz 的 8 核处理器,这可能意味着 可能使用的是GlobalFoundries的工艺,但目前详情尚不清楚。在项目资金中,有三分之二将由“主力客户”(例如 Rostec 和子公司)提供,而最后三分之一将来自联邦预算。这些处理器将进入的系统最初将在俄罗斯教育和科学部以及卫生部运行。Syntacore 已经使用 RISC-V 架构开发了自己的内核,而不是授权设计。关于当前的 RISC-V 设计是否足够强大以用于适合管理服务的日常工作机器一直存在疑问,但是最近有消息称 Canonical 正在某些 SiFive RISC 上启用 Ubuntu/Linux -V 设计,到 2025 年,如果俄罗斯处理器符合任何要求的规范,那么很可能会有足够多的软件选项可供选择。话虽如此,俄罗斯或中国等地的非标准处理器使用较旧的 Linux 定制分支来满足使用硬件的企业的需求并不少见。Sintakor 的文档指出,他们最高性能的 64 位内核已经支持 Linux。这一消息是一个有趣的发展,因为俄罗斯已经有多个本土 CPU 前景正在开发中,例如 Elbrus 2000 系列处理器运行自定义 VLIW 指令集,并为 Intel x86 和 x86-64 进行二进制转换;这些处理器已经提供在 Linux 上运行的 8 核和多插槽系统。Elbrus 的开发仍在进行中,Rostec 参与其中,该项目似乎专注于桌面到服务器使用的高性能实现。相比之下,新的 RISC-V 开发似乎针对台式机和笔记本电脑使用的低功耗实现。俄罗斯也有使用 MIPS32 ISA 的贝加尔湖处理器,由俄罗斯一家超级计算机公司制造。看看这个故事如何发展会很有趣:4 亿美元应该足以构建一个处理器并指导这个级别的系统设计,这就提出了项目执行情况的问题。Compsci eggheads 将 OpenCL 框架引入 RISC-V 以推动并行性能

四位计算机科学专家展示了将 OpenCL 编程框架引入各种 RISC-V 芯片的工作——提高了它们对科学及其他领域高度并行工作负载的适用性。RISC-V 于 2010 年出生于加州大学伯克利分校,遵循 1980 年代早期名为伯克利 RISC 的研究项目,最终成为 SPARC 架构,RISC-V 既免费又开源。因此,任何人都可以构建实现 RISC-V 架构的芯片,并可以随意修改和扩展它,根据需要添加新功能或调整现有功能。然而,在第五届 RISC-V 计算机体系结构研究研讨会 (CARRV 2021) 上发表的一篇论文完全专注于现成的 RISC-V 芯片——介绍了对常用的开放计算语言 (OpenCL) 异构编程框架的支持跨 CPU、GPU 和其他加速器分散科学工作负载。研究人员在论文摘要中解释说:“据我们所知,目前还没有针对开源社区可以访问的商品 RISC-V 处理器的 OpenCL 公开实现。”“除了向现有的丰富多样的科学并行应用程序开放 RISC-V 之外,OpenCL 还提供了对计算机体系结构研究中有用的独特基准类型的访问。”团队研究产生的 OpenCL 实现不需要对处理器设计本身进行任何更改,并且与一系列部件兼容——从高性能多核处理器到低调的嵌入式实现。包括后者被证明是一个挑战:“[这些] 通常不支持原子指令或多线程,”该团队发现。该团队的工作建立在 Performance OpenCL (POCL) 项目之上,这是一个开源 OpenCL 实现,以前针对一系列架构,包括 x86、Arm、MIPS 和通用 GPU (GPGPU) 部件。POCL 首先经过修改,以支持具有 Linux 功能的更高性能 RISC-V 芯片,例如为 SiFive 的HiFive Unmatched提供支持的芯片,然后再转向嵌入式芯片。该团队总结道:“通过 OpenCL 扩展 RISC-V 生态系统以包括并行应用程序,这为科学计算的大领域打开了大门。” “此外,它为硬件设计人员提供了新的工作负载,用于探索新的微架构设计和优化。“我们对 [POCL] 的扩展特别针对当今没有 SIMD 矢量扩展的大量商用 RISC-V 内核,并且还扩展到具有最小功能的低调嵌入式处理器。”这项工作与促进 RISC-V 在科学计算中的存在的其他努力一起进行,包括在 RISC-V 高性能计算特别兴趣小组 (SIG-HPC) 的支持下推进的一些工作。该团队在开放获取条款下发表了其论文 ,而扩展 POCL 的源代码已根据 MIT 许可放在GitHub 上。

*免责声明:以上内容仅供交和流学习之用。如有任何疑问或异议,请留言与我们联系。