队伍编号:CICC1304

系统:win10/Ubuntu20.02 Vivado:2022.2

FPGA:AX7050B

我们采用了XLINX AX7050B型号的开发板来综合E203内核,在这里主要介绍我们的综合过程遇到的问题以及解决方式。

1、新建vivado项目,根据开发板的型号选择xc7s50fgga484-2部分。

2、导入E203的代码,主要是rtl文件夹以及综合顶层文件。使用vivado的clocking wizard实例化一个时钟,来生成E203所需要的两个时钟信号。

3、根据项目需求编写约束文件。

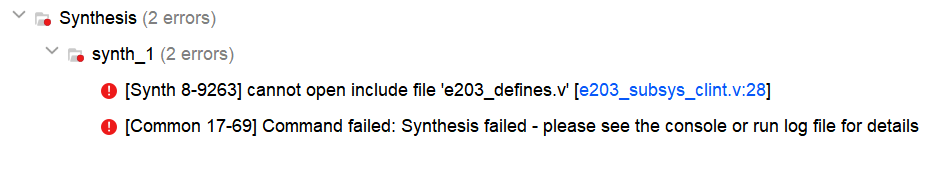

4、运行综合。该过程遇到问题:找不到头文件(如下图)。

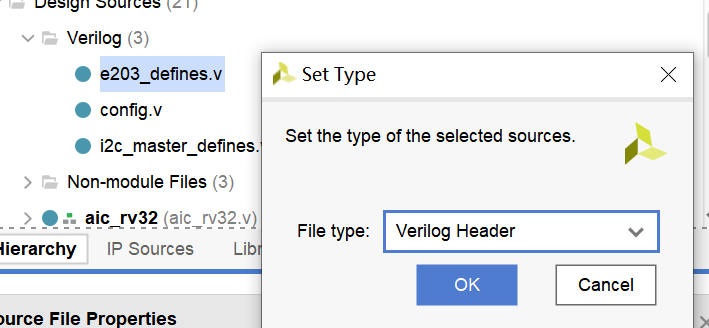

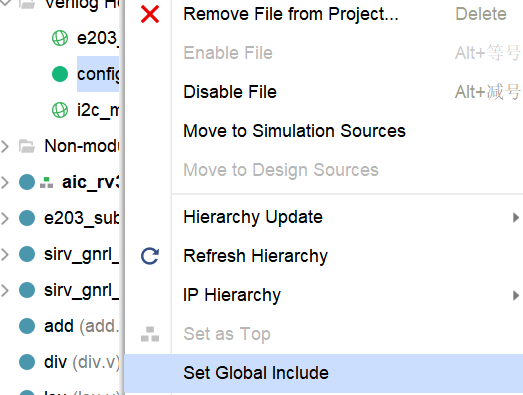

解决方式:将vivado项目下的Verilog目录下的e203_defines.v、config.v、i2c_master_defines.v这三个文件都修改成Verilog Header的类型,并设置成global include属性,如下:

5、综合和实现成功,在生成bit流的时候,出现端口未约束的问题。

解决方式:在生成bit流部分加入如下tcl命令set_property SEVERITY {Warning} [get_drc_checks NSTD-1]set_property SEVERITY {Warning} [get_drc_checks UCIO-1]

6、bit流生成成功后,开启FPGA并连接,在vivado的硬件管理部分找到我们的FPGA,并将bit流通过“Program Device”选项写入到FPGA中。

至此,完成了AX7050B综合E203的整个过程。