队伍编号: CICC3454

队伍名称: 喝可乐队

我们为蜂鸟e203新添加了硬件断点的功能。添加Trigger Module,并实现包括tselect,tdata1~7,tcontrol,tinfo在内的寄存器,在flash模式下可以在IDE中直接设置硬件断点,最多可以支持6个硬件断点(当前硬件版本由于没有这么大的调试需求,先支持2个)。

在调试过程中,断点分为软件断点和硬件断点。软件断点是在运行起来的程序中设置特征值,也就是把断点处的指令先读回Debugger,保存起来,然后把一条特殊指令写到这个地址去,从而在运行时识别。这种方法的优点时数目不受限制,但是由于要写memory,所以不能设置在ROM中。硬件断点,则需要硬件寄存器支持,断点数目受core里面的寄存器个数限制,优点是可以在任意地方设置。

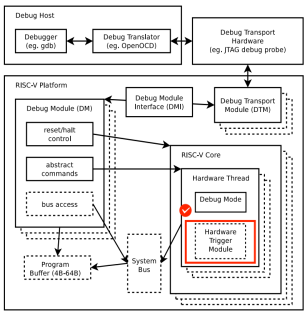

在RISC-V架构下,支持硬件断点的寄存器称为Trigger Register。图1为RISC-V架构的Debug模型,其中Hardware Trigger Module中即包含Trigger Register用于支持硬件断点。设置硬件断点后,断点信息存储于硬件断点寄存器内,程序执行到断点位置时寄存器值于断点条件吻合,CPU中断。同时,发生中断时,需要存储程序PC等到指定寄存器,用于程序的恢复运行。

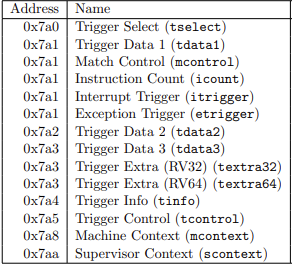

本项目即在RISC-V内核中添加了Hardware Trigger Module,并依据表1所示riscv-debug-release标准设置寄存器地址和内容等信息。在设计时实现了三个用于存储断点信息的硬件断点,tdata1~3寄存器。其中tdata1用于存储控制信息,故最多可设置两个硬件断点。

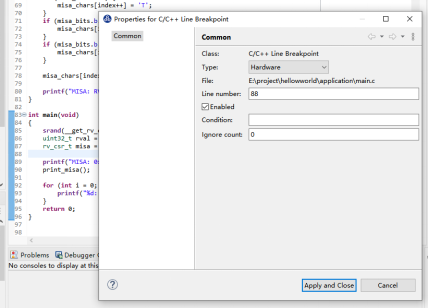

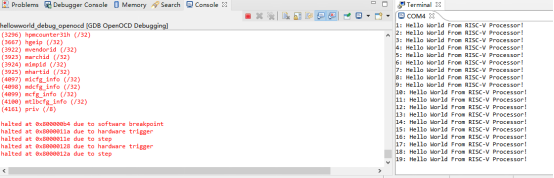

在Nuclei Studio环境下测试时使用选择任一模板程序,如图2所示设置硬件断点,使用Openocd进行Debug,最终程序停在设置的硬件断点位置。继续运行程序,程序将运行到下一断点位置。继续运行,最终程序将执行完毕。测试证明,硬件断点功能添加成功。