一.队伍介绍

队伍编号:CICC1915

本篇文章主要介绍复杂的软件算法硬件IP核的实现

二.具体方法与步骤

通过 C 语言实现软件算法,并验证了算法的有效性以后,就可以进行算法的 HDL 转化工作了。通过使用 Altium Designer 的 CHC 编译器(C to Hardware Compiler)将算法编译转化为可综合的 Verilog 文本,进而通过 FPGA 在硬件上实现算法。

Altium Designer 是 Altium 公司开发的一款电子设计自动化软件,用于电子线路的原理图和印刷电路板(PCB)的设计,并集成了板级设计、现场可编程门阵列 (FPGA)设计和单片机的设计功能。Altium Designer 可用于高速电路板布线,同时还可完成差分对布线。在 2005 年之前,Altium Designer 的名称为 Protel。后来,Altium 公司收购了 PCAD 及 TASKING,使其变成 Altium Designer 的一部分。 Altium Designer 强调“一体化”设计理念:软件和硬件协同设计,硬件设计“软 件化”,电子设计可重用等。这些设计思想是电子设计的趋势。 Altium Designer 除了可以进行传统的电路原理图以及 PCB 设计以外,它还可以进行单片机程序设计以及 FPGA 的开发。在本设计中将 C 语言组件转换为 HDL 描述文件 就是使用 Altium Designer 设计套件中 TASKING 组件的 CHC 编译器完成的。 CHC 编译器,即 C-to-Hardware Compiler。它输入 C 语言源程序然后输出一个可 综合的 FPGA 硬件描述语言,其流程如图 1.1 所示。

图 1.1 CHC 流程

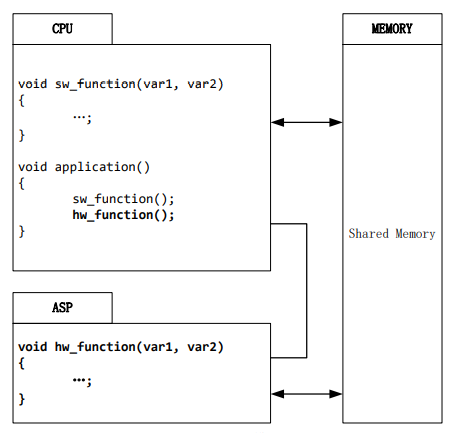

CHC 编译器的应用场景除了直接使用 C 语言进行 FPGA 设计以外,一个重要的应 用场景是如图 1.2 所示。在 SOPC 系统中创建 ASP(Application Specific Processor peripheral component)模块,即和应用相关的专用的处理模块,使用这种模块可以将一 些软件的处理过程转移到全部或部分转移到硬件中完成(起到类是图像处理中的显卡 的作用),从而实现应用处理的加速。

图 1.2 ASP Mode

CHC 编译器将 C 语言源代码编译为 HDL 的过程一共分为两步:

(1) C to HASM

(2) HASM to HDL

第一步 C to HASM 是将 C 语言描述的算法编译为一种中间的、与实际硬件是有一 定的对应关系的“硬件汇编”语言,即 Hardware Assembly(HASM),第二步就将 HASM 文本描述的具体逻辑实现直接翻译成 HDL 文本。在这里主要分享一下 HASM 以及 C to HAL 的实现的技术细节,知道这些技术细节将有利于在使用 C 语言编写算法时实现一些有针对性的优化。

HASM 是一种在 C 语言编译到 HDL 时、经过严格定义的专用的语言模型,它是从传统的计算机汇编语言演变而来,同时它是支持指令集级的并行执行。可以认为 HASM 是一种比 VHDL 或 Verilog 稍微高级一点的硬件描述语言,但是和 C 语言相比,又是一种相对受限的函数功能的简短的描述。

HASM 语言包含了两种结构,一种是功能域一种是结构域。

功能域负责一些基本的运算操作,例如算术运算、逻辑运算还有数据传送操作,通常由组合逻辑实现,并且与 C 语言中的运算符有对应关系。

结构域负责将功能域中的各个基本功能单元按特定的顺序和方式连接起来,通常被实现为一个由有限状态机控制的数据通路,该结构与C 语言的流程控制语句相对应。

以一个简单的加法组合逻辑为例:

__export uint8_t function1(uint8_t a, uint8_t b)

{ return a + b; }

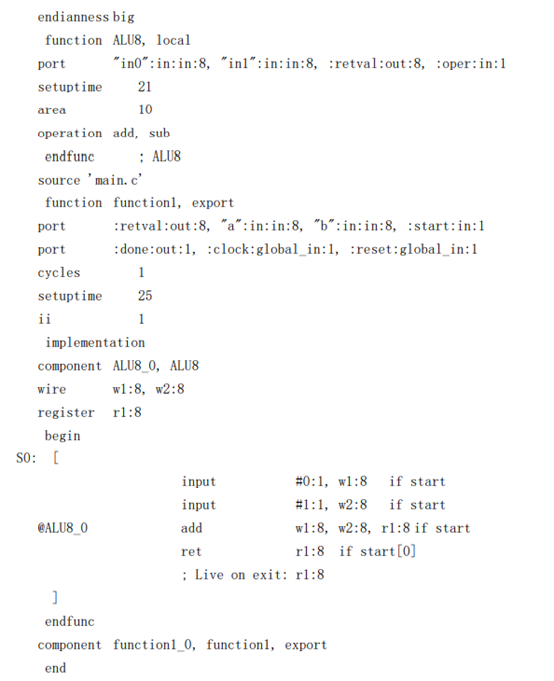

该函数编译后的 HASM 代码如下:

从 HASM 代码的头部可以看到一些整个 模块的一些比较关键的信息,例如建立时间、执行时间以及端口信息等。通过检查一个函数的 HASM 代码,可以大致判断这个函数被综合为硬件电路以后工作所需要的时钟周期数,并且在关键的地方通过查看应的 HASM 汇编指令,可以反过来对 C 语言编写的算法流程提供一定的优化建议。

在HASM 的 implementation 部分,定义了整个模块使用的一个 ALU8 的组合逻辑模块,该模块对应于 C 语言的加法运算符。还有连接 ALU8 以及各个端口的 wire 部件等。

从 begin 到 end 部分,包含了整个函数实现的逻辑实现,由于加法操作上纯粹的组 合逻辑,所以可以看到整个实现只有一个状态“S0”。

对于有复杂时序要求的操作,例如加密算法里面常见的 for 循环结构,在生成 begin 和 end 之间就会有多个状态,每个状态都对应与某个组合逻辑的特定的连接方式,也就是特定的数据通 路。而每一个状态的中的 jmp 指令,主要控制状态之间的转移。

只要能将 C 语言编译为 HASM 语言,接下来的操作就是是将 HASM 语言转化为 HDL 语言。ashc 命令将 HASM 语言转换为 ELF 格式的目标文件,然后由 hdlhc 命令将 目标文件翻译为对应的 HDL 文件。

在编译为“汇编”代码的过程中,使用编译和优化技术将可以并行执行的、没有 前后依赖关系的操作步骤被集中起来对应于一个有限状态机的某一个状态从而实现并 行处理,而运算则对应于一些组合逻辑电路。即将算法转化为一个由有限状态机控制 的数据通路。

一份 C 文件在编译为 HDL 文件时对应于一个模块,而该 C 文件里面的变量、函数 则对应于该模块里面的对象。若一个 C 函数中的数据流比较简单,没有前后的依赖关 系,这个函数就会被转换为纯粹的组合逻辑,否则就是一个同步时序逻辑。一个模块可 以包含若干组合逻辑或者时序逻辑对象,同一个模块里面的所有的时序逻辑对象共享一 个 CLOCK 信号以及 RESET 信号,但每一个时序逻辑对象都有一个独立的 START 信号 用于控制该对象是否开始运行以及用于指示操作完成的 DONE 信号。函数的参数以及 返回值则作为该对象的输入输出信号。

软件算法硬件加速 IP 核 HDL 文件的生成分为两个步骤,首先根据将要接入的 SOPC 系统的总线的特性,将算法做适当的包装、暴露相关的接口以及调用方法, 即适配总线接口。不同的 SOPC 总线有不同的时序以及数据传输规则,而 C 语言则只有函数调用以及变量,因此需要根据总线信号的不同,将 C 语言编写的算法做一定的包装,最后再使用 C to Hardware 技术完成 HDL 文件的生成。

本文分享通过一种直接使用标准 C 语言进行 FPGA 硬件开发的方法,设计、实现了软件算法的硬件 IP 核。