修订历史

| 版本号 | 修订日期 | 修订的章节 | 修订的内容 |

|---|---|---|---|

| 1.0 | 2020/03/4 | N/A | 初始版本 |

用户将通过本文,快速掌握从ARM Cortex-M内核MCU(下文简称:CM_MCU)迁移至Nuclei N级别内核MCU(下文简称:N_MCU)嵌入式软件应用开发的必要知识点。包括:内核及MCU的背景知识介绍、芯来软件平台NSP应用介绍、嵌入式软件应用开发实例解析及集成开发环境等内容。

中断和异常应用,是N级别内核应用中的重点和难点。本文讲结合嵌入式软件应用开发实例,着重讲解,N级别内核的中断和异常使用方法。通过对例程解析,使用户在最短的时间内,熟练掌握N_MCU的嵌入式软件应用项目开发。

为了使用户能对以上介绍的应用实例,进行快速启动和实践操作。本文将基于芯来科技推出的RV-STAR开发板,介绍通过芯来软件平台NSP进行应用实例的调试运行流程。

本手册相关代资源包下载地址:N系列内核MCU软件移植资料包

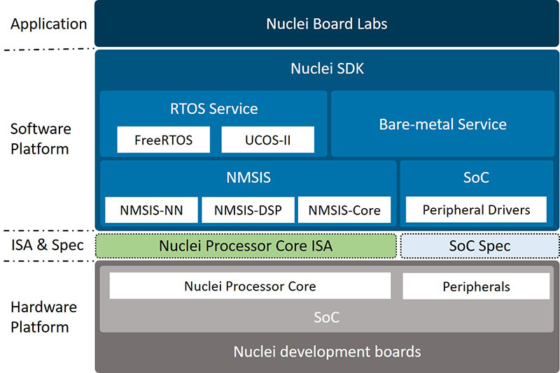

芯来软件平台NSP(Nuclei Software Platform)包括:

Nuclei微控制器软件接口标准(NMSIS:Nuclei Microcontroller Software Interface Standard)。

Nuclei处理器内核的软件开发包(Nuclei SDK: Nuclei Software Development Kit )。

Nuclei SDK是专为基于芯来科技Nuclei处理器内核的SoC开发的软件开发包。Nuclei SDK以NMSIS为基础进行开发,提供NMSIS上的所有功能,包括NMSIS-Core,NMSIS-NN,NMSIS-DSP。Nuclei SDK提供裸机(Bare-metal)以及实时操作系统(FreeRTOS,μC/OS-II)开发环境。

请参阅芯来科技官网在线文档页面(https://doc.nucleisys.com/nuclei_sdk)《Nuclei-SDK’s documentation》了解其详情。

NMSIS是为芯来科技RISC-V处理器定义的厂商无关的硬件抽象层,定义了通用工具接口并提供持续的处理器设备支持,以及简洁的处理器和外设的软件访问接口API。采用NMSIS框架,可以大幅提升应用软件的复用性,缩短RISC-V微处理器开发者的学习时间,缩短基于芯来内核IP的新产品的上市时间。

请参阅芯来科技官网在线文档页面(https://doc.nucleisys.com/nmsis)《NMSIS’s documentation》了解其详情。

Nuclei Board Labs,由Nuclei Board Labs软件包及RV-STAR开发板组成。

Nuclei Board Labs是基于Nuclei SDK开发的适配RV-STAR开发板的实验教程,提供手把手的实验手册,方便RV-STAR开发板使用者入门以及教学使用。通过实验教程将有助于开发者更好的理解和使用Nuclei SDK以及了解NMSIS标准。

关于Nuclei Board Labs,请参阅芯来科技官网在线文档页面(https://doc.nucleisys.com/nuclei_board_labs)了解其详情。

RV-STAR是一款基于GD32VF103 MCU的RISC-V评估开发板。GD32VF103系列器件是基于Nuclei Bumblebee处理器的32位通用微控制器。

关于GD32VF103 MCU芯片的相关内容,请参阅RISCV-MCU网站下载页面下载《GD32VF103 RISC-V 32-bit MCU Datasheet》和《GD32VF103 RISC-V 32-bit MCU用户手册》。

关于芯来RV-STAR开发板,请参阅RV-Star开发板介绍页面了解其详情。

SEGGER Embedded Studio(以下简称SES)是SEGGER公司推出的一款嵌入式开发的集成开发环境,具有开发与编译界面专业,调试功能强大(配备知名的J-Link仿真器),非商业使用免费,跨平台兼容和配置灵活等特点。

下文中的移植实例解析将使用SES为IDE,介绍在RV-STAR开发板上进行嵌入式软件的开发。

关于使用SES进行基于RV-STAR的快速开发详细信息,详情请参见SES for RV-STAR快速上手手册。

Nesting_of_interrupts程序是一个完整的示例程序,它使用到了SoC系统中的外设,调用了中断服务程序等。

下文将使用基于CM_MCU实例程序,移植到基于N_MCU 示例程序。

原实例工程基于ARM Cortex-M内核MCU STM32F4系列MCU。

移植到基于Nuclei N内核GD32VF103系列 MCU(RV-STAR开发板)。

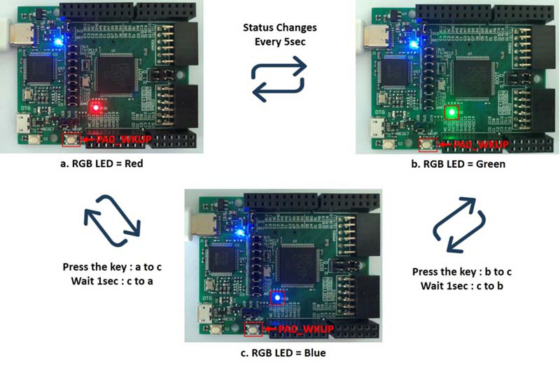

该程序功能简述如下:

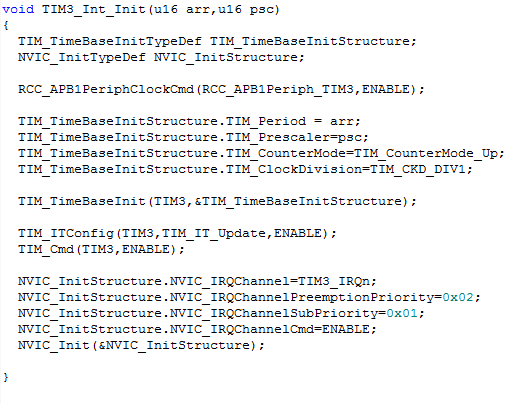

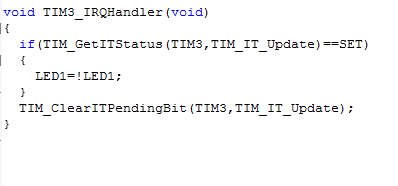

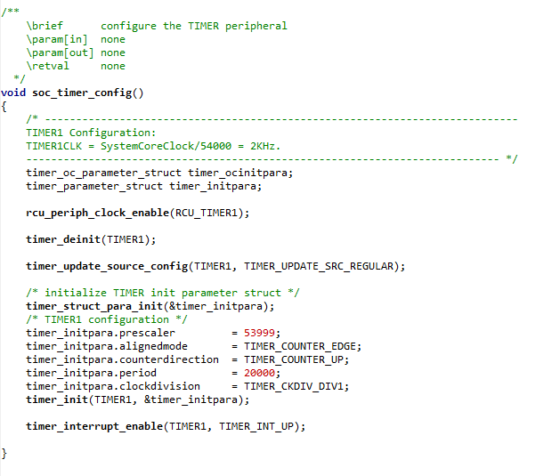

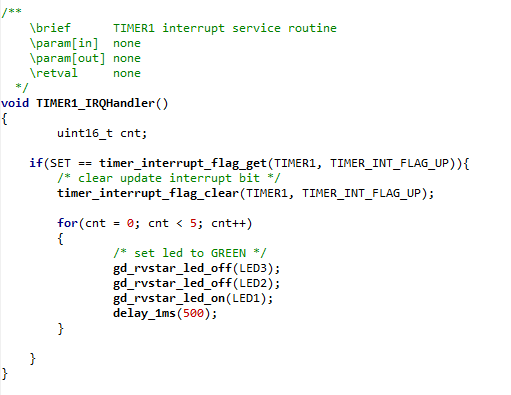

设置一个TIMER定时器(SoC

TIMER),使其周期性的产生一个定时器中断。在定时器中断中点亮绿色LED(熄灭红色和蓝色LED),并调用延时函数(使用N_MCU的CORE

TIMER实现),进行1s延时。

CORE TIMER:N级别处理器内核私有计时器单元(Timer Unit,TIMER),与ARM Cortex-M内核的SysTick功能相同 。关于CORE TIMER的详细信息,请参见第7章“延伸阅读”第7.1节了解详情。

SoC TIMER:CM_MCU及N_MCU的SoC外设,定时器模块。

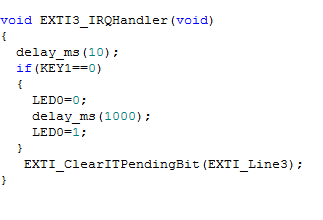

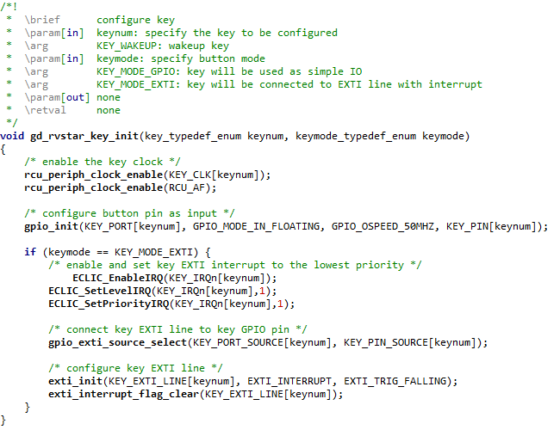

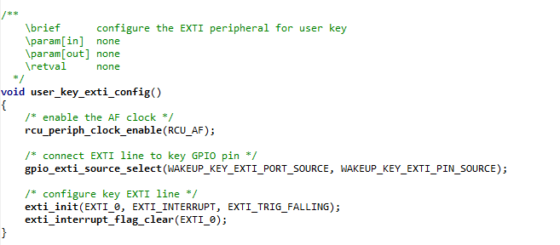

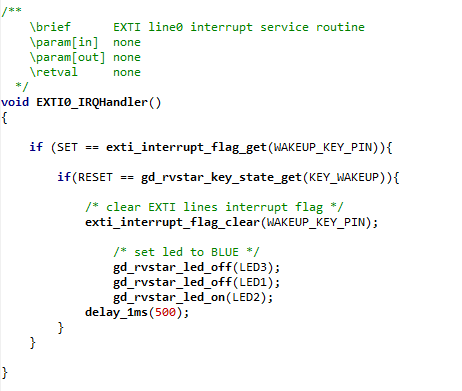

设置一个用户按键中断,作为一个ECLIC的外部中断,在其中断服务程序中会将点亮蓝色LED(熄灭红色和绿色LED),并调用延时函数,进行5s延时。

进入死循环后,循环点亮红色LED(熄灭绿色和蓝色LED)。

演示效果如下图所示:(基于RV-STAR开发板) RGB LED颜色每隔5s在红色和绿色间切换;若按下用户按键,RGB LED切换到蓝色,1s后切换为之前的颜色。

用户可以通过以下下载链接获取本文移植实例的工程源码。

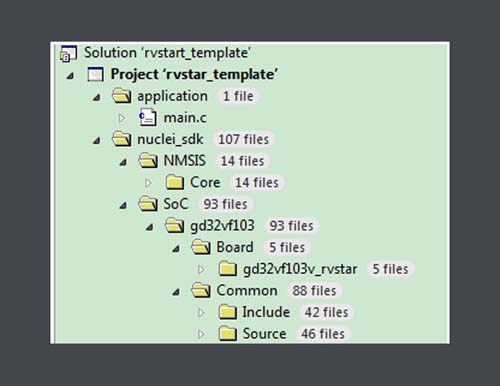

第一步:使用SES IDE导入rvstart_template工程模板(该模板基于Nuclei SDK)。

第二步:移植CM_MCU实例中SysTick功能至N_MCU的CORE TIMER功能。

第三步:移植CM_MCU实例中NVIC功能至N_MCU的ECLIC、异常和NMI功能。

第四步:移植CM_MCU实例中SoC外设功能至N_MCU 对应的外设功能。

下文将分别予以简述。

使用SES IDE导入rvstart_template工程模板。

application文件夹下main.c,为用户的main函数。

nuclei_sdk文件夹下,包含NMSIS库函数(类似CM_MCU的CMSIS库函数)和SoC库函数文件夹(本实例基于RV-STAR开发板,包含gd32vf103相关的库函数)。

(注意:为了方便用户对比CM_MCU和N_MCU的实例工程,下文中将rvstart_template的工程名称修改为:nesting_of_interrupts)

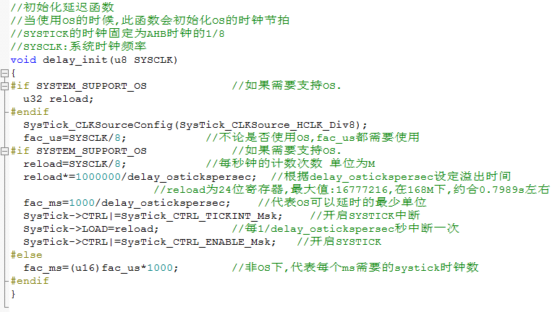

ARM Cortex-M内核包含了一个SysTick定时器,SysTick 是一个24 位的倒计数定时器,当计到0 时,将从RELOAD 寄存器中自动重装载定时初值。只要不把它在SysTick 控制及状态寄存器中的使能位清除,就永不停息。在本实例中,将利用STM32F4的内部SysTick来实现延时函数功能,这样既不占用中断,也不占用系统定时器。

delay_init函数即为使用SysTick进行延时的功能函数,该函数位于nesting_of_interrupts\SYSTEM\delay\delay.c中,其代码如下:

(注意:当用户需要运行RTOS时,SysTick通常被用来提供系统时钟节拍)

N级别处理器内核包含的CORE TIMER,主要用于产生计时器中断(Timer Interrupt)和软件中断(Software Interrupt)。在本实例中,将利用GD32VF103内部的计时器单元来实现延时函数功能。

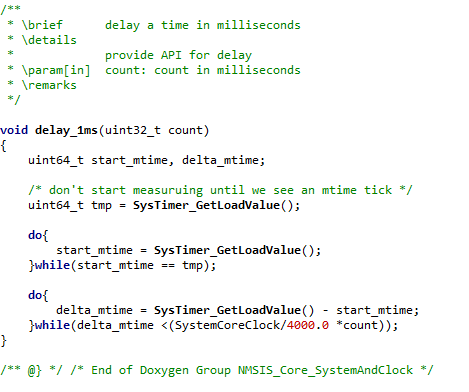

delay_1ms函数即为使用CORE TIMER进行延时的功能函数,该函数位于ses_nuclei_sdk_projects\nuclei-sdk\SoC\gd32vf103\Common\Source\system_gd32vf103.c中,其代码如下:

(注意:当用户需要运行RTOS时,CORE TIMER通常被用来提供系统时钟节拍。)

关于CORE TIMER的详细信息,请参见第7章“延伸阅读”第7.1节了解详情。

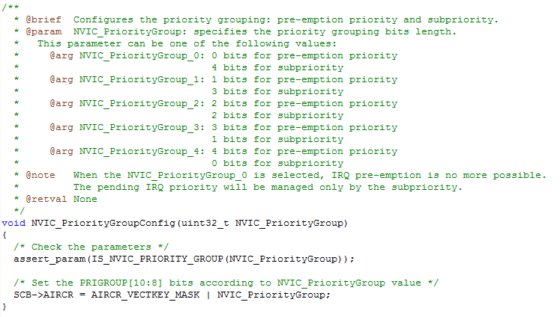

ARM Cortex-M内核包含的NVIC的全称是Nested vectoredinterrupt controller,即嵌套向量中断控制器。

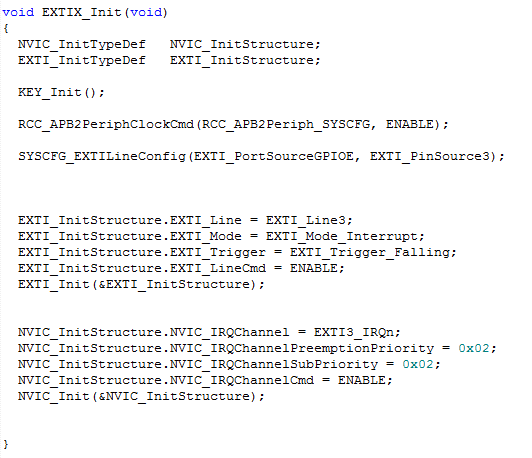

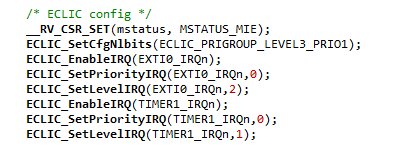

本实例中,NVIC管理了两个中断:定时器中断和外部中断(用户按键)。

N级别处理器内核包含的ECLIC,可用于多个中断源的管理。N级别处理器内核中的所有类型(除了调试中断之外)的中断都由ECLIC统一进行管理。

关于ECLIC的详细信息,请参见第7章“延伸阅读”第7.2节了解详情。

NVIC负责管理内核中断(异常和NMI)。

ECLIC不负责管理异常和NMI。

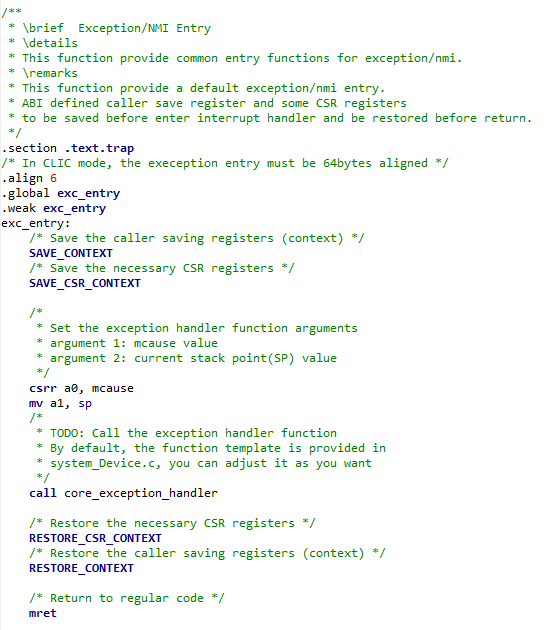

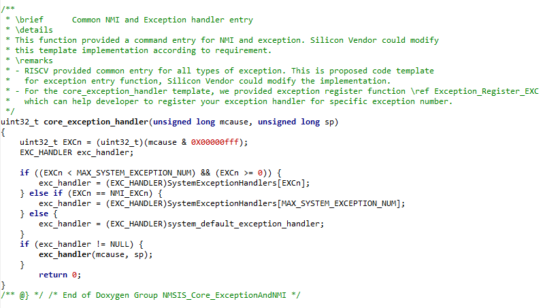

在Nuclei SDK中已经将异常和NMI处理的基础框架实现,使得普通应用开发人员无需关心底层这些细节。其中对于异常和NMI处理基础框架实现介绍如下:

关于异常的详细信息,请参见第7章“延伸阅读”第7.3节了解详情。

关于NMI的详细信息,请参见第7章“延伸阅读”第7.4节了解详情。

在CM_MCU实例工程中,SoC外设功能的初始化函数文件,位于HARDWARE文件夹下;SoC外设功能库函数文件,位于FWLIB文件夹下。

用户可以根据项目需要,添加外设初始化函数文件,以及添加FWLIB库文件进行库函数调用。

在N_MCU实例工程中,SoC外设功能的初始化函数文件和库函数文件,位于nuclei-sdk\SoC\gd32vf103文件夹下,用户可以方便的进行SoC外设功能的初始化和功能库函数的调用。

请参阅芯来科技在线文档页面(https://doc.nucleisys.com/nuclei_board_labs)了解其详情。

Segger Embedded Studio IDE (for RISC-V)

J-Link(Debugger for RISC-V)

请参阅芯来科技官网下载页面(http://www.nucleisys.com/download.php)下载《Nuclei_SES_IDE_Installation.pdf》和《SES for RV-STAR快速上手手册》。

I-jet (Debugging and trace probes for RISC-V)

请参阅IAR

SYSTEMS官网页面(https://www.iar.com/iar-embedded-workbench/#!?architecture=RISC-V) 和(https://www.iar.com/iar-embedded-workbench/add-ons-and-integrations/in-circuit-debugging-probes/#!?currentTab=i-jet) 进行详细了解。

N级别处理器内核包含CORE TIMER,主要用于产生计时器中断(Timer Interrupt)和软件中断(Software Interrupt)。

详情请参见:https://doc.nucleisys.com/nuclei_spec/isa/timer.html

N级别处理器内核包含的ECLIC,用于管理所有的中断源。

详情请参见:https://doc.nucleisys.com/nuclei_spec/isa/eclic.html

异常(Exception)机制,即处理器核在顺序执行程序指令流的过程中突然遇到了异常的事情而中止执行当前的程序,转而去处理该异常。

详情请参见:https://doc.nucleisys.com/nuclei_spec/isa/exception.html

NMI(Non-Maskable

Interrupt)是处理器内核的一根特殊的输入信号,往往用于指示系统层面的紧急错误(譬如外部的硬件故障等)。在遇到NMI之后,处理器内核应该立即中止执行当前的程序,转而去处理该NMI错误。

详情请参见:https://doc.nucleisys.com/nuclei_spec/isa/nmi.html

Nuclei ISA标准规范,是为用户准备的Nuclei RISC-V ISA文档,包括完备的Nuclei RISC-V特性文档和完备的Nuclei Processor Core Unit文档。通过标准规范的文档学习,开发者可快速了解Nuclei RISC-V处理器特性,并用于研发项目中。

详情请参见:https://doc.nucleisys.com/nuclei_spec

Nuclei SDK是专为基于芯来科技Nuclei处理器内核的SoC开发的软件开发包。Nuclei SDK以NMSIS为基础进行开发,提供NMSIS上的所有功能,包括NMSIS-Core,NMSIS-NN,NMSIS-DSP。Nuclei SDK提供裸机(Bare-metal)以及实时操作系统(FreeRTOS,μC/OS-II)开发环境。

详情请参见:https://doc.nucleisys.com/nuclei_sdk

NMSIS是为芯来科技RISC-V处理器定义的厂商无关的硬件抽象层,定义了通用工具接口并提供持续的处理器设备支持,以及简洁的处理器和外设的软件访问接口API。采用NMSIS框架,可以大幅提升应用软件的复用性,缩短RISC-V微处理器开发者的学习时间,缩短基于芯来内核IP的新产品的上市时间。

详情请参见:https://doc.nucleisys.com/nmsis

配合Nuclei SDK及RV-STAR开发板的配套实验教程(Nuclei Board Labs),方便开发者快速上手及应用。